PXA270Ƕ��ʽϵ�y�OӋ(2)���r犼���λ����

�r�g��2016-12-09���ߣ��A���hҊ

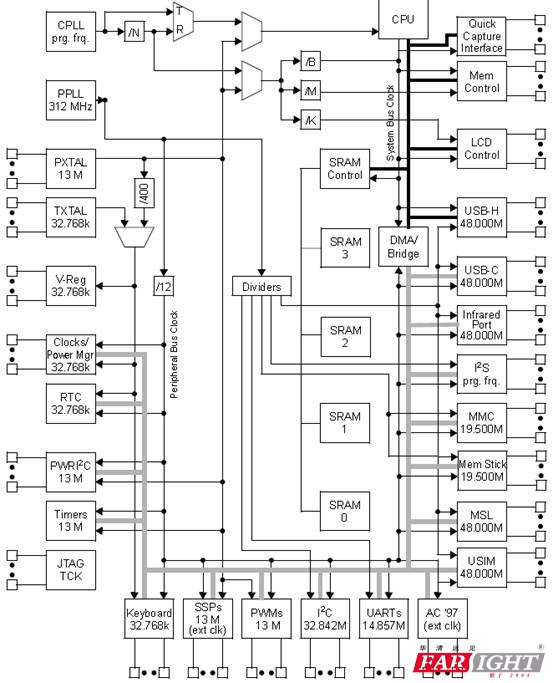

��Ӌ��ᘌ��҂��A���hҊ�Ľ̌W�_�lһ��PXA270ϵ�y���Ұ��ҵ�һЩܛ��Ӳ���_�l�^��ӛ����ʹ��һ�������ӑՓ���кõĽ��h���һ��Ҫ���r������lht@farsight.com.cn����һƪ�Ҍ���“PXA270Ƕ��ʽϵ�y�OӋһ���Դ��������”�����������һ���P�ڕr犼���λ���ֵă��ݣ��gӭָ��~~ һ���r犲��� �κ�һ��̎��������Ҫ����һ���r�Դ����̎�����ăȲ����������ĕr犹����Ԫ���cpu���������ܿ��Ɔ�Ԫ�ṩ���m�ĕr犡� PXA270̎��������Ҫ�ɂ��ⲿ��ʎ����1��13M��1��32.768K���������Ե����ã�

PXA270̎�����Ȳ��Ѓɂ�PLL��Ԫ��һ�������PLL����һ���Ǻ���PLL

�r犲��ֵ��·ԭ��D��

������λ���� PXA270�ṩ��5�N��λ��ʽ��

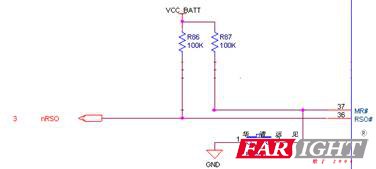

ϵ�y�к͏�λ���P���·ԭ��D��

�D��max1586C��ϵ�y��λ�·���P�ĽӾ�

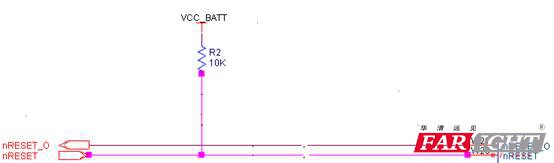

K1���λ���I��ͨ�^max1586C�ď�λ�����·ݔ��nRSO��̖�����ϵ�y�]�����max1586C�ď�λ�����·��Ԓ��������һƬ���max811�ď�λоƬ����ɣ�Ҳ���������ݼ�һЩ߉�·�ķ�ʽ����ɏ�λ�� ע�⣺max1586C��MR�_��λ����λmax1586C��V3ݔ����1.3V��������늉�ݔ���]��Ӱ푡� �D�Ǐ�λ��̖��PXA270��nRESET�ĽӾ���

��nRESET��λ���T����������λ�r��nRESET_O��������λ���������������������оƬ�ď�λ�� �D��JTAG�·�����λ��̖Ҫ��ϵ�y��nRESET�B�ӡ�

�r犏�λ���ִ��¾��@ô���ˡ�

���P�YӍ

�l���uՓ

|